- Welcome to Trenz Electronic GmbH Support Forum.

Recent posts

#21

Trenz Electronic FPGA Modules / Flash memory on TE0710 from Mi...

Last post by gapbesides - March 21, 2024, 08:02:19 AMI attempted to use QSPI to write to the module's flash memory, but I'm having trouble getting the right data to be stored there. The written data has incorrect bytes at the beginning.

I made every effort to see if the page alignment of the memory was the cause of the issue, but I was unable to resolve it even by moving the address I obtained from figuring out the start address of a page. Does anyone have any past writing experience with this device?

I made every effort to see if the page alignment of the memory was the cause of the issue, but I was unable to resolve it even by moving the address I obtained from figuring out the start address of a page. Does anyone have any past writing experience with this device?

#22

Trenz Electronic FPGA Modules / Re: Si5338 TE0713

Last post by JH - March 13, 2024, 02:07:46 PMHi,

project is included into the reference design download, see post from Manuela:

https://wiki.trenz-electronic.de/display/PD/TE0712+Test+Board#TE0712TestBoard-Download

br

John

project is included into the reference design download, see post from Manuela:

QuoteFor the TE0712 series we have a reference design with the Si5338A-B which you can find in the following link--> Follow Wiki Download Link:

- https://wiki.trenz-electronic.de/display/PD/TE0712+Test+Board

You can then find the corresponding clock-builder reference project in

- <project_folder>\test_board\misc\PLL\SI5338

https://wiki.trenz-electronic.de/display/PD/TE0712+Test+Board#TE0712TestBoard-Download

br

John

#23

Trenz Electronic FPGA Modules / Re: Clock on TE0715-05-51I33-A

Last post by MA - March 08, 2024, 08:28:28 AMHi Michael,

we will answer you by email.

br

we will answer you by email.

br

#24

Trenz Electronic FPGA Modules / Re: Si5338 TE0713

Last post by ame - March 05, 2024, 01:48:06 PMHello,

I need to configure TE0713 si5338. I'm looking for TE0713 clock-builder project.

Thank you for your help.

Regards

I need to configure TE0713 si5338. I'm looking for TE0713 clock-builder project.

Thank you for your help.

Regards

#25

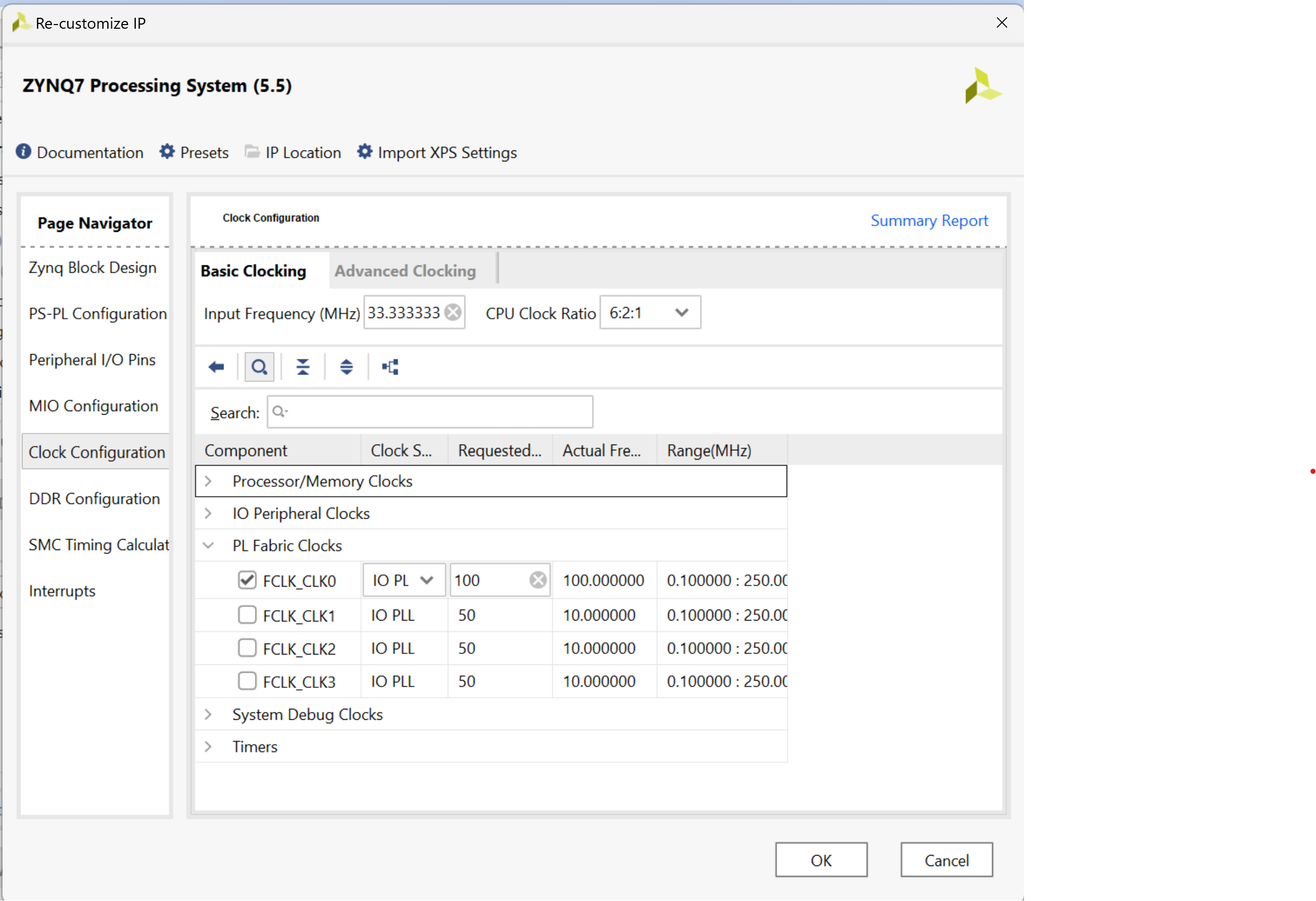

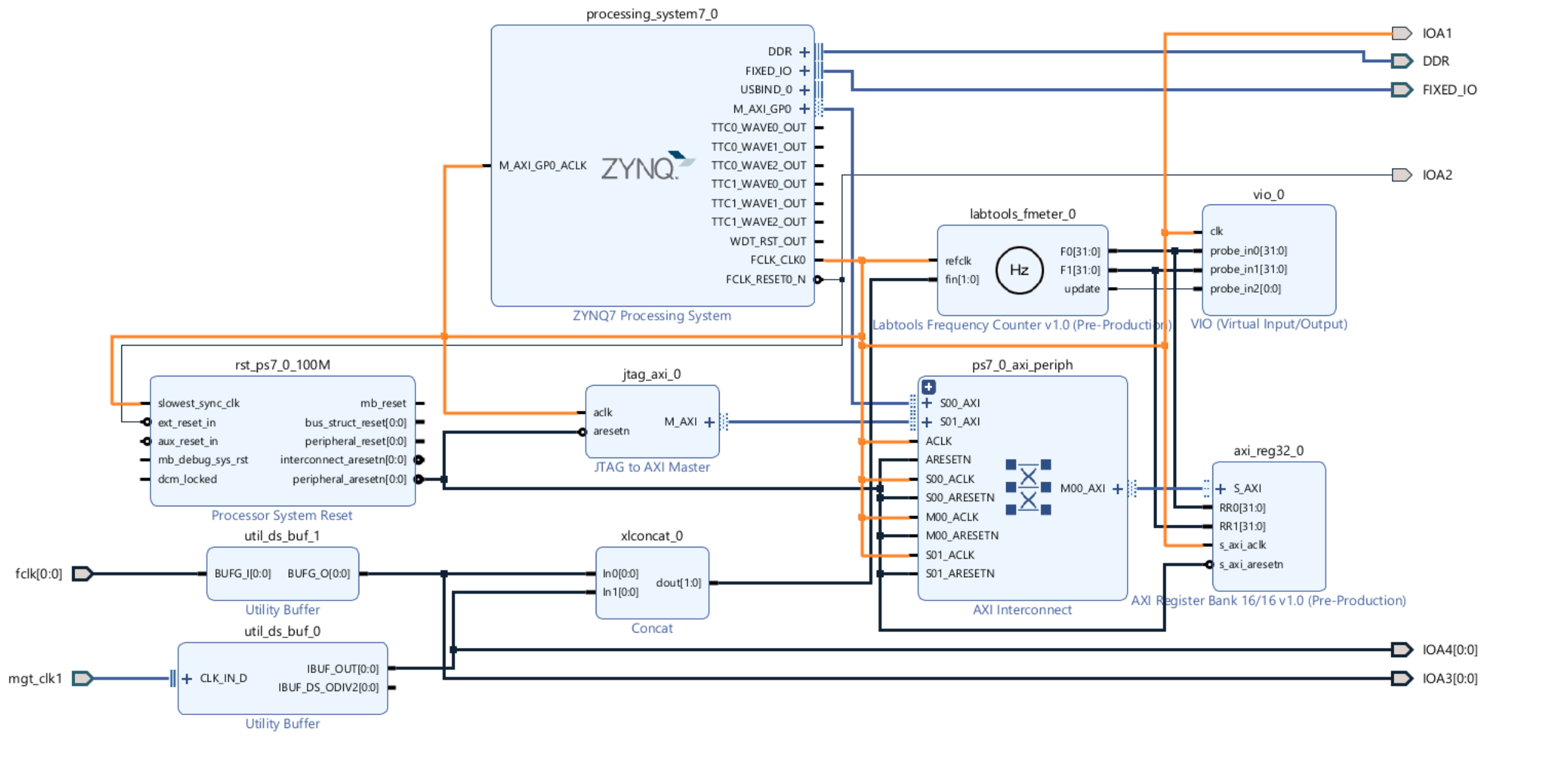

Trenz Electronic FPGA Modules / Clock on TE0715-05-51I33-A

Last post by Michael - March 05, 2024, 11:32:49 AMDear,

We are working with an TE0715-05-51I33-A FPGA on the TE0705 carrier board. When running the example project, there seems to be no clock going to the PL. We measure

inputs:

fclk[0] : no clock

mgt_clk1 : clock signal (as expected)

PS outputs:

FCLK_CLK0 : no clock, constant high

FCLK_RESET0_N : low (active!)

We verified that the programming works and the measured pins are connected correctly by implementing some simple asynchronous logic.

We made no modifications to the TE0705 carrier board other than adjusting the output voltages to 3V3. According to our understanding of the documentation, this should work. We did not modify the example vivado project except adding output pins to measure the previously mentioned signals.

Does somebody have an idea what the problem could be? Is there some reset we don't see that stops the clock from being produced?

We are working with an TE0715-05-51I33-A FPGA on the TE0705 carrier board. When running the example project, there seems to be no clock going to the PL. We measure

inputs:

fclk[0] : no clock

mgt_clk1 : clock signal (as expected)

PS outputs:

FCLK_CLK0 : no clock, constant high

FCLK_RESET0_N : low (active!)

We verified that the programming works and the measured pins are connected correctly by implementing some simple asynchronous logic.

We made no modifications to the TE0705 carrier board other than adjusting the output voltages to 3V3. According to our understanding of the documentation, this should work. We did not modify the example vivado project except adding output pins to measure the previously mentioned signals.

Does somebody have an idea what the problem could be? Is there some reset we don't see that stops the clock from being produced?

#26

Trenz Electronic FPGA Modules / Re: Si5338 TE0713

Last post by MA - March 05, 2024, 10:53:12 AMHello,

what exactly do you want to do? TE0712 and TE0713 are two different series and therefore cannot be compared 1:1.

For the TE0712 series we have a reference design with the Si5338A-B which you can find in the following link

- https://wiki.trenz-electronic.de/display/PD/TE0712+Test+Board

You can then find the corresponding clock-builder reference project in

- <project_folder>\test_board\misc\PLL\SI5338

We do not currently have a reference design for the TE0713 series that includes the Si5338.

Best regards,

Manuela

what exactly do you want to do? TE0712 and TE0713 are two different series and therefore cannot be compared 1:1.

For the TE0712 series we have a reference design with the Si5338A-B which you can find in the following link

- https://wiki.trenz-electronic.de/display/PD/TE0712+Test+Board

You can then find the corresponding clock-builder reference project in

- <project_folder>\test_board\misc\PLL\SI5338

We do not currently have a reference design for the TE0713 series that includes the Si5338.

Best regards,

Manuela

#27

Trenz Electronic FPGA Modules / Re: Si5338 TE0713

Last post by ame - March 04, 2024, 02:09:06 PMQuote from: ame on March 04, 2024, 02:07:37 PMHello,(The Schematic change from TE012 to TE013.)

I'm trying to configure SI5338. I getback the TE0712 ClockBuilder project, but it looks the schematic changed. The termination resistor R49 has been add on clk3 (200MHZ) and remove on CLK (125MHz).

Should I change the format output on clock builder pro?

Could you provide your clock-builder reference project?

I'm using Vhdl project https://github.com/steffenmauch/SI5338-VHDL but I obtain 87.63MHz instead of 100MHz.

Regards

#28

Trenz Electronic FPGA Modules / Si5338 TE0713

Last post by ame - March 04, 2024, 02:07:37 PMHello,

I'm trying to configure SI5338. I getback the TE0712 ClockBuilder project, but it looks the schematic changed. The termination resistor R49 has been add on clk3 (200MHZ) and remove on CLK (125MHz).

Should I change the format output on clock builder pro?

Could you provide your clock-builder reference project?

I'm using Vhdl project https://github.com/steffenmauch/SI5338-VHDL but I obtain 87.63MHz instead of 100MHz.

Regards

I'm trying to configure SI5338. I getback the TE0712 ClockBuilder project, but it looks the schematic changed. The termination resistor R49 has been add on clk3 (200MHZ) and remove on CLK (125MHz).

Should I change the format output on clock builder pro?

Could you provide your clock-builder reference project?

I'm using Vhdl project https://github.com/steffenmauch/SI5338-VHDL but I obtain 87.63MHz instead of 100MHz.

Regards

#29

MAX1000 community projects / Playing ZX Spectrum in HDMI in...

Last post by Subcritical - February 22, 2024, 05:52:24 AMPlaying great new games:

https://itch.io/s/111036/full-pat-morita-pack

Capture playing Shovel Adventure:

https://youtu.be/uP6nl9aS-cw

New 4Mbytes Sdram to Sram Wrapper:

https://github.com/AtlasFPGA/zx/blob/main/atlas.max/sdram.v

New DVI/HDMI Wrapper in verilog:

https://github.com/AtlasFPGA/zx/blob/main/atlas.max/hdmi.v

#30

Trenz Electronic FPGA Modules / ZX Spetrum in MAX1000

Last post by Subcritical - February 22, 2024, 05:46:02 AMPlaying great new games:

https://itch.io/s/111036/full-pat-morita-pack

Capture playing Shovel Adventure:

https://youtu.be/uP6nl9aS-cw

New 4Mbytes Sdram to Sram Wrapper:

https://github.com/AtlasFPGA/zx/blob/main/atlas.max/sdram.v

New DVI/HDMI Wrapper in verilog:

https://github.com/AtlasFPGA/zx/blob/main/atlas.max/hdmi.v

https://itch.io/s/111036/full-pat-morita-pack

Capture playing Shovel Adventure:

https://youtu.be/uP6nl9aS-cw

New 4Mbytes Sdram to Sram Wrapper:

https://github.com/AtlasFPGA/zx/blob/main/atlas.max/sdram.v

New DVI/HDMI Wrapper in verilog:

https://github.com/AtlasFPGA/zx/blob/main/atlas.max/hdmi.v